GUC UCIe 64G IP在台积电N3P上完成设计定案

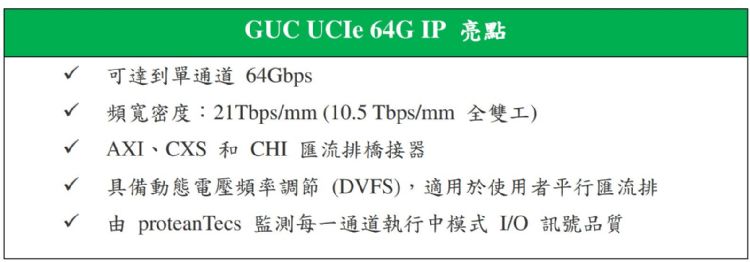

先进特殊应用集成电路 (ASIC)领导厂商创意电子(GUC)近日宣布成功推出业界领先Universal Chiplet InterconnectExpress (UCIe)实体层芯片,实现UCIe规格定义中每通道64Gbps的最高速度。

创意电子的UCIe 64G IP支持UCIe 3.0,能提供每1公厘晶粒边缘21Tbps(10.5 Tbps/mm全双工)的惊人带宽密度。创意电子藉助于台积电的先进N3P技术和CoWoS先进封装来达成此一里程碑,旨在锁定AI、高效能运算(HPC)、数据中心和网络等应用领域。

为了方便整合,GUC利用UCIe串流通讯协定,开发了适用于AXI、CXS和CHI汇流排的桥接器。这些桥接器经过最佳化,具备高流量密度、低延迟和低功率的特色,搭配高效率的端对端流量控制,促进从单芯片 NoC架构到小芯片系统的无缝转变。它们支持动态电压频率调节(DVFS),实现数码供应电压和汇流排频率的实时变化,同时确保数据流不会中断。

创意电子的UCIe IP也备有多项进阶可靠性功能,包括UCIe Preventive Monitoring(预防性监控)功能,以及由proteanTecs提供的整合式I/O信号品质监控功能。

这项技术可在无需重新训练或中断操作的情况下,对数据传输期间的信号完整性进行不间断的任务模式监控,不仅可独立监控每个信号通道,还能实时侦测功耗和信号完整性异常。如此即可及早识别凸块和传输线缺陷,借此触发修复演算法,以透过备援I/O取代接近临界点的I/O,从而防止系统故障。此一主动积极的方式可大幅延长芯片的使用寿命,并强化系统可靠性。

创意电子技术长Igor Elkanovich表示:「基于台积电先进的制程与封装技术,我们致力推出效能最高、功耗最低的2.5D/3D小芯片及HBM界面IP。2.5D与3D封装技术现在都趋向使用HBM3E/4/4E、UCIe-A和UCIe-3D界面,有助于开发出超越光罩尺寸限制的高度模块化处理器,进而为新一代的高效能运算铺路。我们与台积电及其开放创新平台(OIP)生态系统的紧密合作,使我们的客户能够在当今人工智能驱动的竞争市场中加快产品上市速度」