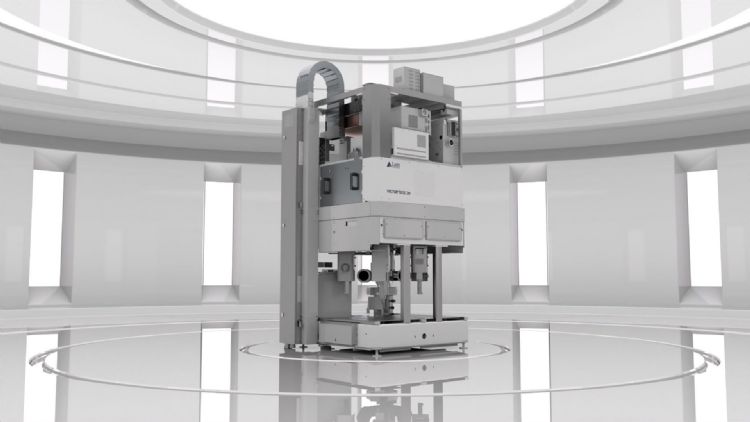

Lam Research科林研发推出VECTOR TEOS 3D 解决芯片制造中关键的先进封装难题

Lam Research科林研发发布VECTOR TEOS 3D,这是一款突破性的沉积设备,专为下时代人工智能(AI)和高效能运算(HPC)应用所需芯片的先进封装而设计。

TEOS 3D旨在解决3D堆叠和高密度异质整合中的关键挑战。它采用专有翘曲晶圆片传送方案、介电沉积创新技术,并借助科林研发Equipment Intelligence技术增强监测能力,可实现超厚且均匀的芯片间介电层填充。目前,TEOS 3D已在全球领先的逻辑芯片和存储器晶圆厂投入使用。

科林研发全球产品事业群资深副总裁Sesha Varadarajan 表示,VECTOR TEOS 3D能沉积业界最厚且无空隙的芯片间介电层填充薄膜,可根据先进芯片堆叠整合方案的高难度需求进行定制化,即便在超高应力、高翘曲的晶圆片也能适用。

这是我们领先业界的先进封装解决方案组合中又一强大成员,它所提供的差异化原子级创新,能协助芯片制造商突破摩尔定律限制,迈向AI时代。

人工智能的爆炸性成长,推动市场支持日益庞大数据工作负载的新型元件需求。芯片制造商正采用3D先进封装技术,将多个芯片整合到小芯片(chiplet)架构中,以实现AI运算能力。透过将存储器与处理单元更紧密结合、最佳化电路路径,小芯片设计可提升处理速度,并在更小的尺寸中整合更高效能。

然而,随着小芯片堆叠高度增加并变得更复杂,一系列的制造新挑战随之出现,制程中的应力可能导致晶圆扭曲或翘曲,薄膜中的裂缝与空隙可能引发缺陷并降低良率。

TEOS 3D克服了先进封装生产中的多项关键挑战,能精准且可靠地处理厚重、高翘曲的晶圆片。它以纳米级精度在芯片间沉积厚度达60微米的专用介电薄膜,且具备沉积厚度超过100微米薄膜的扩展能力。这类薄膜提供关键的结构、热力学和机械强度支撑,防止层状结构剥离等常见封装失效问题。

此外,TEOS 3D也搭载了科林研发独创的翘曲晶圆载盘技术和最佳化的晶圆载盘设计,在处理厚晶圆时能提供卓越稳定性,即便面对极端晶圆翘曲,也能实现均匀的薄膜沉积。

更有其他亮点,能以单次制程沉积厚度超过30微米且无裂缝薄膜的解决方案,大幅提升良率并缩短制程时间。以独特的Quad-Station模块(QSM)架构提升生产力:科林研发经过验证的QSM架构透过4个独立反应机构实现平行处理,减少瓶颈问题。模块化设计使其产能相较科林研发上一代介电层填充解决方案提升近70%,并提升高达20%的拥有成本效益。

及科林研发Equipment Intelligence技术实现制程可重复性:内建于TEOS 3D的Equipment Intelligence 解决方案,透过智能技术监测制程、快速解决问题并自动化例行任务,可提升设备效能与可靠性,进而提升良率。与更高的能源效率,能整合高效率射频产生器和节能模式外设控制,在提升制程精度的同时降低耗能。

凭藉在先进封装领域15年的领导地位,以及在介电薄膜数十年的专业经验,TEOS 3D建立在科林研发已有的VECTOR Core和TEOS产品系列之上,标志着在整合封装材料与制程的持续创新。它是科林研发全面产品组合的一部分,该组合提供业界领先的解决方案,解决关键挑战,并推动先进封装工作流程中的创新与生产力提升。

- 以精准量测驱动半导体创新Renishaw三大技术亮眼SEMICON Taiwan

- 中勤SEMICON2025展会成果丰硕 2026年陆续投产 共迎智能制造新时代

- 美商盛美半导体推面板级先进封装设备 创新技术成半导体展关注焦点

- SK海力士开始供应移动端NAND快闪存储器解决方案ZUFS 4.1

- G2C联盟五周年 携手抢攻AI浪潮 打造台湾先进封装自主化新格局

- AI与永续并进 半导体产业展现永续承诺

- 从配角变核心!AI算力爆发驱动存储器大跃进

- 欧姆龙亮相SEMICON Taiwan 引领半导体检测技术革新

- 筑波携手奈微光亮相SEMICON Taiwan展出半导体与矽光子解决方案

- ATEN参与2025国际半导体展

- 台达亮相SEMICON Taiwan展示半导体软硬整合与网安方案

- Lam Research科林研发推出VECTOR TEOS 3D 解决芯片制造中关键的先进封装难题

- 亚泰致力研磨液设备智能化 从问题本质出发创造半导体制程新价值

- 广化科技隆重发表AI智能甲酸回焊炉 实现高可靠度功率模块组装

- 先进制程搭配先进封装 引领新时代高效能芯片

- FOPLP具备成本、效率、设计灵活优势 掀起先进封装新革命

- 中勤SEMICON 2025聚焦国际交流 以Panel FOUP与EFEM引领自动化新标准

- 志圣工业抢攻AI封装商机 跨足多元应用布局未来十年成长

- 协助半导体厂从节能到良率 展绿科技揭示能源数据的制程价值

- Renishaw 亮相 SEMICON Taiwan:精密量测引领半导体制程革新